01.Chiplet助力半导体弯道超车

1、Chiplet优势

摩尔定律指引过去几十年集成电路产业发展。摩尔定律由英特尔创始人之一的戈登·摩尔(Gordon Moore)提出,其核心内容为:在价格不变时,集成电路上可以容纳的晶体管数量每18-24个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降为之前的一半。在过去几十年,摩尔定律指引着集成电路产业发展。随着工艺进步,集成电路上晶体管密度不断提升,驱动计算机性能保持几何级数增长,而性能的快速提升则推动芯片价格迅速下降。

“摩尔定律”发展陷入瓶颈,集成电路进入后摩尔时代。从1987年的1um制程至2015年的14nm制程,集成电路制程迭代大致符合“摩尔定律”的规律。但自2015年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm制程的量产进度均落后于预期。随着台积电宣布2nm制程工艺实现突破,集成电路制程工艺已接近物理尺寸的极限,摩尔定律发展陷入瓶颈,行业进入了“后摩尔时代”。

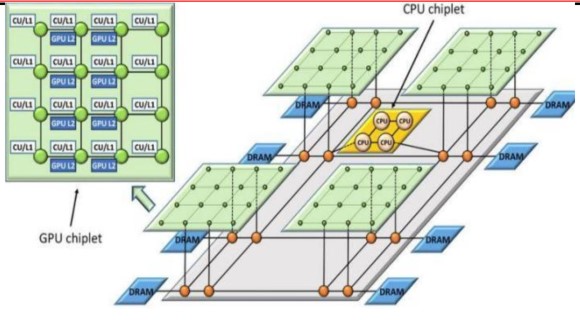

Chiplet可在不改变制程的前提下提升算力,且保证芯片良率。Chiplet俗称“芯粒”,又称“小芯片组”,从字面意义上可以理解为“粒度更小的芯片”。它是将一类满足特定功能的die,通过die-to-die内部互联技术实现多个模块芯片与底层基础芯片封装在一起,进而形成一个系统芯片。它可以有效提升芯片的集成度,是在不改变制程的前提下提升算力,并且保证芯片生产良率的一种手段。

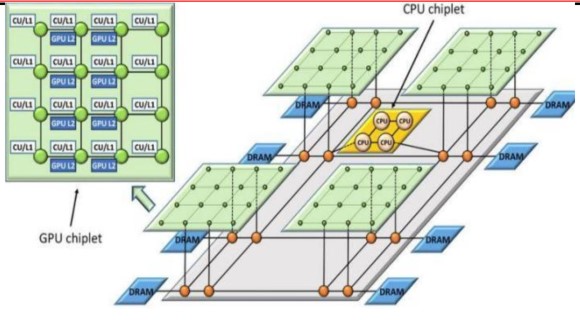

图表1:GPU、CPUChiplet示意图

数据来源:电子工程世界

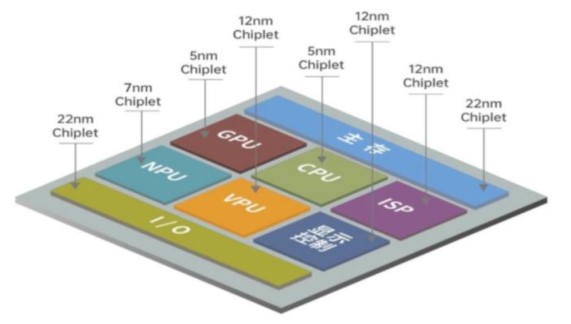

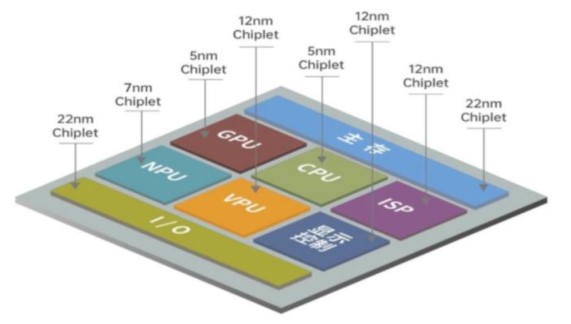

图表2:集成多制程工艺器件的Chiplet异构处理器

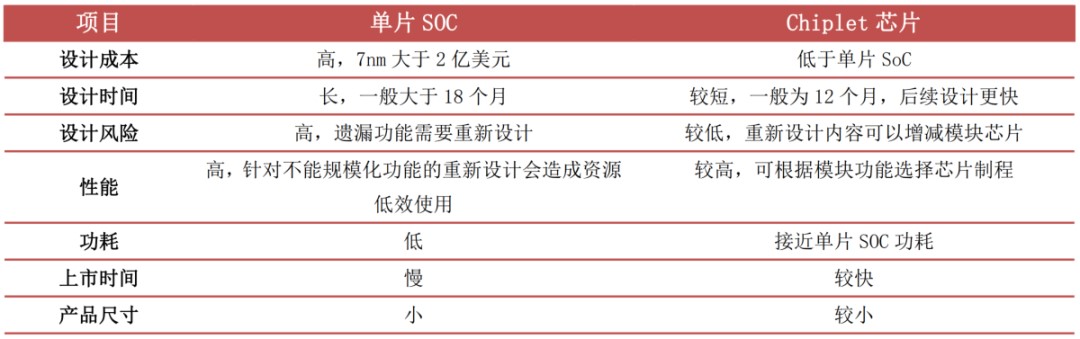

与传统SoC相比,Chiplet在设计灵活度、设计与生产成本、上市周期等方面优势明显。传统SoC,即系统级单芯片,是将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上。随着摩尔定律放缓,传统的SoC的生产周期越来越长,在成本大幅增加的情况下性能提升幅度有限,行业接近制造瓶颈;与SoC不同,Chiplet是将一块原本复杂的SoC芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯片组。

相比传统的SoC,Chiplet能够有效降低研发、设计与制造成本,并显著提升芯片良率。英特尔公司高级副总裁、中国区董事长王锐在2022世界集成电路大会上表示,Chiplet技术是产业链生产效率进一步优化的必然选择。“不但提高芯片制造良品率,利用最合适的工艺满足数字、模拟、射频、I/O等不同技术需求,而且更将大规模的SoC按照不同的功能,分解为模块化的芯粒,减少重复的设计和验证环节,大幅度降低设计复杂程度,提高产品迭代速度。且有利于后续的产品迭代,缩短上市周期。”

Chiplet优势一:降低芯片设计的复杂程度,有效降低研发与设计成本。Chiplet芯粒设计灵活,且可重复使用,通过将已知的合格芯片裸片进行集成,能够缩短芯片的研发与设计周期,降低研发设计成本。据悉,设计28nm芯片的平均成本为4,000万美元,设计7nm芯片的成本上升至2.17亿美元。而The Linley Group的白皮书《Chiplets Gain Rapid Adoption:Why Big Chips Are Getting Small》中提出,Chiplet技术可以将大型7nm设计的成本降低25%。

Chiplet优势二:提升良率。SoC将多个不同类型计算任务的计算单元以光刻形式集成在同一片晶圆上,随着先进制程不断推进,单位面积上集成的晶体管数量越来越多,设计周期越来越长,芯片面积也在加大。高性能计算等领域巨大运算需求推动逻辑芯片运算核心数量上升,配套SRAM容量、I/O数量随之提升。随着芯片面积的加大和集成的晶体管数量增多,对制造过程中的芯片良率提出较高挑战,让芯片生产中的工艺误差和加工缺陷显得愈发明显,一个微小的缺陷就可能导致整个大芯片报废。Chiplet技术将大芯片分割成不同功能模块进行独立制造,通过将广泛的、成熟的芯片裸片进行集成,只需保障各个被集成的成熟芯片良率即可,能够降低先进制程的研发与制造风险,有效提升良率。

Chiplet优势三:大幅降低芯片制造成本。SoC中的逻辑计算单元对性能要求高,整体依赖先进制程,具有极高的生产壁垒与制造成本;Chiplet方案则可针对不同的模块采取不同的合适的制程,分开制造,最后采用先进封装技术进行组装,能大幅降低芯片的制造成本。

后摩尔时代,Chiplet成为提高芯片算力与集成度的重要途径。后摩尔时代,随着集成度提升,SoC开始在供电、功耗和散热等方面面临挑战,芯片全流程设计成本大幅增加,而制程工艺接近极限,每次迭代升级都需要付出极大的额外成本,而随着性能提升,发热功耗等方面的问题也日益凸显,继续追求极致工艺的意义已经不大。Chiplet作为当下较受关注的半导体发展方向,可有效降低能够有效降低芯片设计与制造的门槛,提升良率和节约成本,因此成为摩尔定律趋缓背景下提升芯片集成度与算力的重要途径。

图表:Chiplet芯片与SoC比较

2、海外科技领域制裁加剧,Chiplet助力国内半导体产业弯道超车

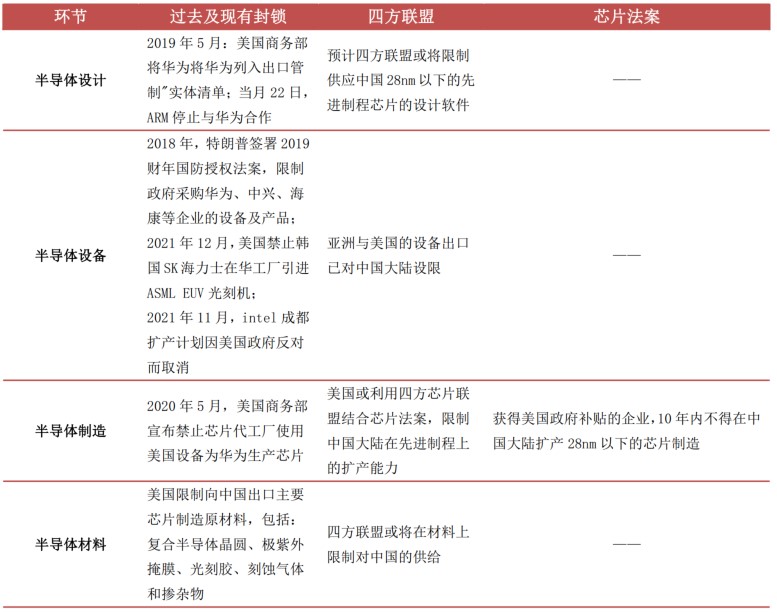

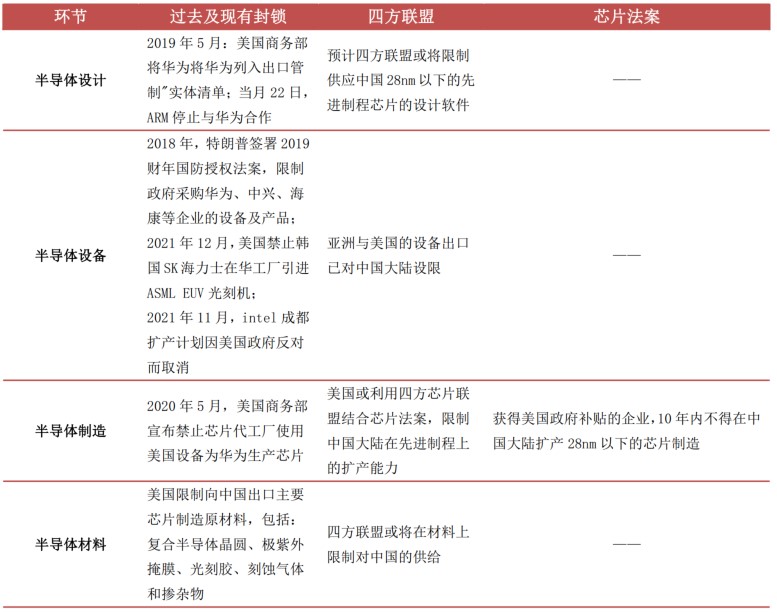

海外科技领域制裁加剧,国内半导体先进制程发展受限。近年来中美摩擦加剧,美国针对中国在高科技领域的限制增多,企图通过加大制裁力度来限制国内集成电路产业发展。2020年12月,美国将中芯国际列入“实体清单”,限制企业14nm及以下半导体制程的扩产;2022年8月,美国签署《芯片与科学法案》,主要用于增强美国本土晶圆厂的竞争力,并明确规定获得美国政府补贴的企业,10年内不得在中国大陆扩产28nm以下的芯片制造。《芯片法案》的签署,进一步加剧了中美在高科技领域的脱钩程度,导致国内芯片先进制程发展受到限制。

图表6:海外制裁限制我国半导体产业发展

数据来源:《中美战略竞争下两岸半导体产业发展问题研究》,美国商务部

先进制程是提高算力的必要途径,台积电先进制程占比不断提高。近年来,人工智能、大数据、自动驾驶和AIoT等下游应用的不断发展,对芯片处理与运算能力提出更高的要求,高性能、低功耗成为先进制程的发展方向。从全球晶圆代工龙头台积电的各制程营收占比来看,近年来台积电先进制程营收占比不断提升:2022年前三季度,台积电实现营收6,131.4亿元新台币,其中5nm制程占比28%,7nm制程占比26%。而分地区看,近年来台积电来自大陆市场的营收占比有所下滑。2022年,美国市场成为台积电最大来源,营收规模达1.49万亿新台币,占比65.96%,中国大陆市场营收2,451.68亿元,占比10.82%,相比2020年的17.45%大幅下滑。

海外制裁加剧,Chiplet有望助力国内半导体产业实现弯道超车。通过先进制程可实现芯片性能的迅速提升,因此全球晶圆代工龙头先进制程占比不断提升,而中国大陆先进制程发展受到限制。Chiplet技术仅对核心Chip采用先进制程,其他如存储芯片、I/O芯片采用成熟制程,有效降低对先进制程的依赖,有望成为我国半导体产业弯道超车的突破口。2022年12月,我国第一个原生Chiplet技术标准——《小芯片接口总线技术要求》团体标准正式发布,这个标准涵盖了多种应用场景的小芯片接口总线技术要求,包括总体概述、接口要求、链路层、适配层、物理层和封装要求等,能够灵活应对不同的应用场景、适配不同能力的技术供应商。《总线技术要求》的发布,对于我国集成电路产业延续“摩尔定律”,打破先进制程限制因素,提升产业综合竞争力,具有重要意义。

3、新互联标准提供行业规范,Chiplet市场规模有望快速扩张

新互联标准UCle出台,为集成不同芯片提供标准与技术支持。尽管Chiplet优势明显,但由于过去Chiplet互联标准并不统一,各类Chiplet产品接口有所不同,无法“拼接”在一起,因此行业发展受到制约。2022年3月,AMD、英特尔、台积电、三星、美光、微软、Meta、Google等十余家半导体、互联网行业巨头联合成立了Chiplet标准联盟,正式推出了通用Chiplet高速互联标准“Universal Chiplet Interconnect Express”(通用芯粒互连,简称“UCIe”),旨在定义一个开放、可互操作的Chiplet生态系统标准。业内巨头联手推动Chiplet接口规范的标准化,以实现Chiplet在封装级别的普遍互联,构建开放的Chiplet生态系统,有助于Chiplet行业快速发展。

UCle是唯一具有裸片间接口堆栈的标准,成为Chiplet设计的首选标准。此前为应对Chiplet设计中所面临的挑战,行业出现了集中不同的标准,但UCle是唯一具有完整裸片间接口堆栈的标准,其他标准都没有为协议栈提供完整裸片间接口的全面规范,大多仅关注在特定层。而且UCIe支持2D、2.5D和桥接封装,预计未来还会支持3D封装。新思科技(Synosys)指出,Ucle的堆栈本身拥有三层:

协议层:最上层为协议层,通过基于流量控制单元(FLIT)的协议实现,确保最大效率和降低延迟,支持最流行的协议,包括PCIExpress®(PCIe®)、Compute Express Link(CXL)和/或用户定义的流协议;

中间层:用于对协议进行仲裁与协商,以及通过裸片间适配器进行连接管理。基于循环冗余检查(CRC)和重试机制,该层还包括可选的错误纠正功能;

物理层:定义了与封装介质的电气接口,是电气模拟前端(AFE)、发射器和接收器以及边带通道允许两个裸片之间进行参数交换与协商的层级。逻辑PHY实现了连接初始化、训练和校准算法,以及测试和修复功能。

图表9:Ucle产业联盟董事会成员

国内厂商纷纷加入,直接受益于Chiplet发展趋势。Ucle的提出,为集成不同制程工艺、不同厂商、不同技术的芯片提供了标准与技术支持,让晶圆代工厂可以对不同类型的芯片进行集成,有助于Chiplet行业快速走向成熟。经过数年发展,Chiplet技术已逐渐走向商用,成为芯片厂商较为依赖的技术手段,也被认为是未来芯片行业发展的重要方向。截至目前,芯原股份、长电科技、OPPO、阿里巴巴等众多国内知名企业已加入UCle联盟中,直接受益于相关技术标准,共同构建Chiplet生态体系,助力行业快速发展。

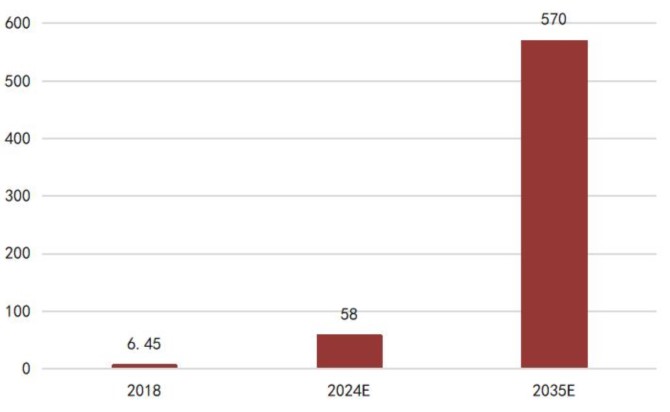

Chiplet市场规模不断扩张,预计2034年有望达到570亿美元。Chiplet可在一定程度上避免摩尔定律放缓的窘境,全球半导体龙头企业积极推进,市场规模有望实现高速增长。Omdia指出,2018年全球chiplet市场规模约为6.45亿美元,至2024年将达到58亿美元,预计到2035年有望突破570亿美元,2018-2035年复合增长率超过30%。

图表11:全球Chiplet芯片市场规模预测(亿美元)